UNDIPUNDIP

Transient: Jurnal Ilmiah Teknik ElektroTransient: Jurnal Ilmiah Teknik ElektroSaat ini pentingnya miniaturisasi dimensi pada perangkat elektronik telah memaksa produsen untuk berinovasi pada struktur dan mekanisme hantaran dari transistor. Junctionless FET (JLFET) telah menunjukkan potensi lebih pada skala dimensi dengan mengurangi kebutuhan source dan drain, berbeda dengan Silicon-On-Insulator (SOI MOSFET). SOI MOSFET masih membutuhkan source dan drain dalam struktur fisisnya. Tugas akhir ini berfokus pada membandingkan kinerja threshold voltage (Vt) dan subthreshold slope (SS) dari JLT dari JLFET dan SOI MOSFET menggunakan Silvaco TCAD 2007. Hasil penelitian menunjukkan bahwa dalam subhtreshold slope (SS), JLFET memiliki nilai ideal sebesar 60 mV/decade, yang unggul dari SOI MOSFET untuk tingkat doping yang sama. Di samping itu, threshold voltage (Vt) menunjukkan kecenderungan yang berbeda antara kedua jenis perangkat. Variasi parameter gate length (Lg), thickness of gate oxide (tox), thickness of silicon (tsi), dan doping concentration (NA) dilakukan pada struktur SOI MOSFET dan JLFET untuk mengetahui trend variasi tersebut terhadap threshold voltage dan substhreshold swing.

Telah berhasil dirancang struktur MOSFET jenis SOI-based, JLT-based, JLT-in situ gate, dan JLT-metal gate menggunakan perangkat lunak Silvaco TCAD 2007 dengan panjang gerbang 50nm, 100nm, dan 200nm.Struktur SOI memiliki trend dimana nilai tegangan ambang berbanding lurus dengan kenaikan panjang gerbang.Sedangkan pada struktur JLT memiliki trend dimana kenaikan tegangan ambang berbanding terbalik dengan nilai panjang gerbang.Semua jenis struktur pada perancangan terjadi penurunan nilai SS ketika panjang gerbang semakin tinggi.Hal ini disebabkan karena muncul SCE, yaitu efek dimana ketika panjang gerbang mengecil makan terjadi kenaikan nilai SS.

Berdasarkan hasil penelitian, terdapat beberapa arah penelitian lanjutan yang dapat dilakukan. Pertama, perlu dilakukan studi lebih lanjut mengenai pengaruh material gate yang berbeda pada kinerja JLT, terutama untuk mengeksplorasi material dengan work function yang lebih optimal untuk meningkatkan kecepatan switching. Kedua, penelitian dapat difokuskan pada optimasi struktur JLT dengan mempertimbangkan efek short channel, misalnya dengan mengintegrasikan teknik doping 3D atau penggunaan high-k dielectric untuk mengurangi efek ini. Ketiga, simulasi dapat diperluas dengan mempertimbangkan efek variasi proses fabrikasi (process variation) terhadap kinerja perangkat, sehingga desain menjadi lebih robust dan dapat diandalkan dalam kondisi produksi yang sebenarnya.

| File size | 425.91 KB |

| Pages | 8 |

| DMCA | Report |

Related /

UNKRISUNKRIS Strategi penataan yang direkomendasikan meliputi optimasi struktur ruang, revitalisasi fungsi resapan, pengembangan waterfront rekreasi, promosi kepadaStrategi penataan yang direkomendasikan meliputi optimasi struktur ruang, revitalisasi fungsi resapan, pengembangan waterfront rekreasi, promosi kepada

UNDIPUNDIP Waktu enkripsi dan dekripsi tercepat dicapai dengan panjang kunci 128 bit, sedangkan waktu enkripsi dan dekripsi terlama dicapai dengan panjang kunci 256Waktu enkripsi dan dekripsi tercepat dicapai dengan panjang kunci 128 bit, sedangkan waktu enkripsi dan dekripsi terlama dicapai dengan panjang kunci 256

UNDIPUNDIP Didapat rata-rata error sebesar 0,087 cm dari hasil yang diinginkan, dengan demikian hasil pengujian melebihi set point, hal ini dikarenakan adanya gangguanDidapat rata-rata error sebesar 0,087 cm dari hasil yang diinginkan, dengan demikian hasil pengujian melebihi set point, hal ini dikarenakan adanya gangguan

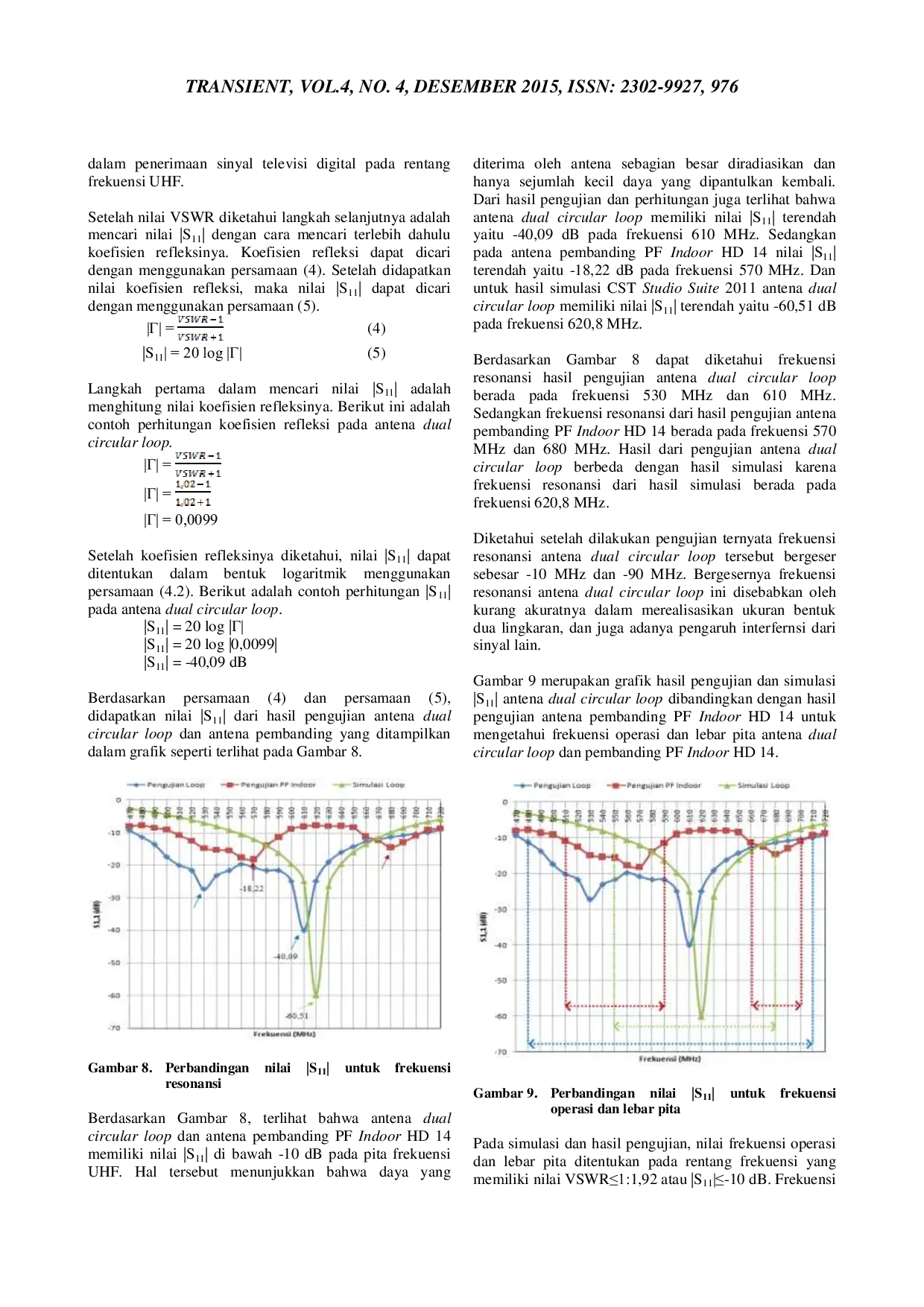

UNDIPUNDIP Penelitian ini berhasil merancang dan memfabrikasi antena dual circular loop directional dengan nilai VSWR yang mendekati ideal, return loss yang sangatPenelitian ini berhasil merancang dan memfabrikasi antena dual circular loop directional dengan nilai VSWR yang mendekati ideal, return loss yang sangat

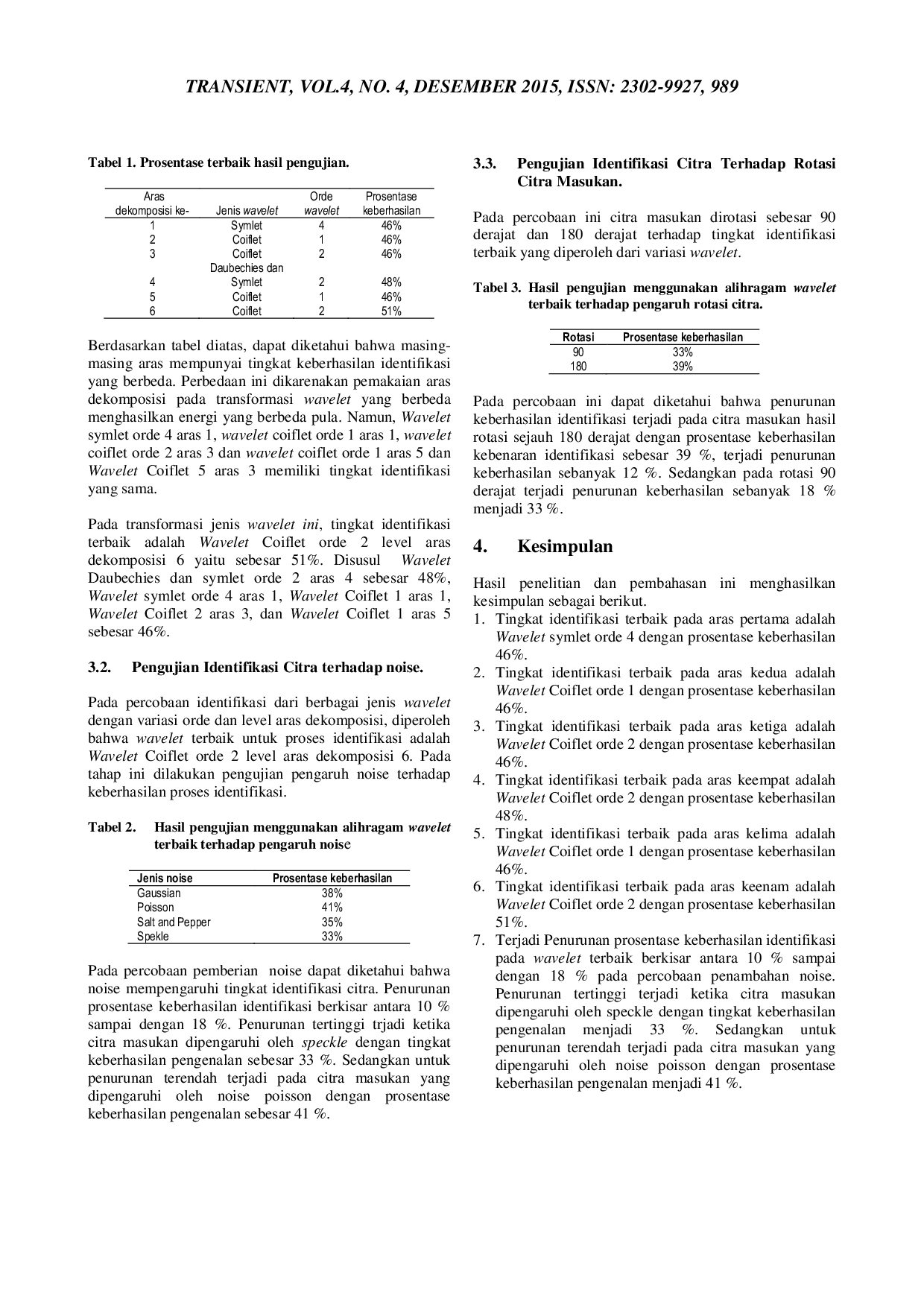

UNDIPUNDIP Proses identifikasi menggunakan perhitungan jarak Euclidean. Pengujian dilakukan terhadap citra uji yang dipengaruhi oleh noise dan rotasi. Hasil pengujianProses identifikasi menggunakan perhitungan jarak Euclidean. Pengujian dilakukan terhadap citra uji yang dipengaruhi oleh noise dan rotasi. Hasil pengujian

UNDIPUNDIP Berdasarkan hasil dan analisis yang sudah dilakukan maka dapat disimpulkan beberapa hal sebagai berikut. Penempatan reflektor untuk mendapatkan keluaranBerdasarkan hasil dan analisis yang sudah dilakukan maka dapat disimpulkan beberapa hal sebagai berikut. Penempatan reflektor untuk mendapatkan keluaran

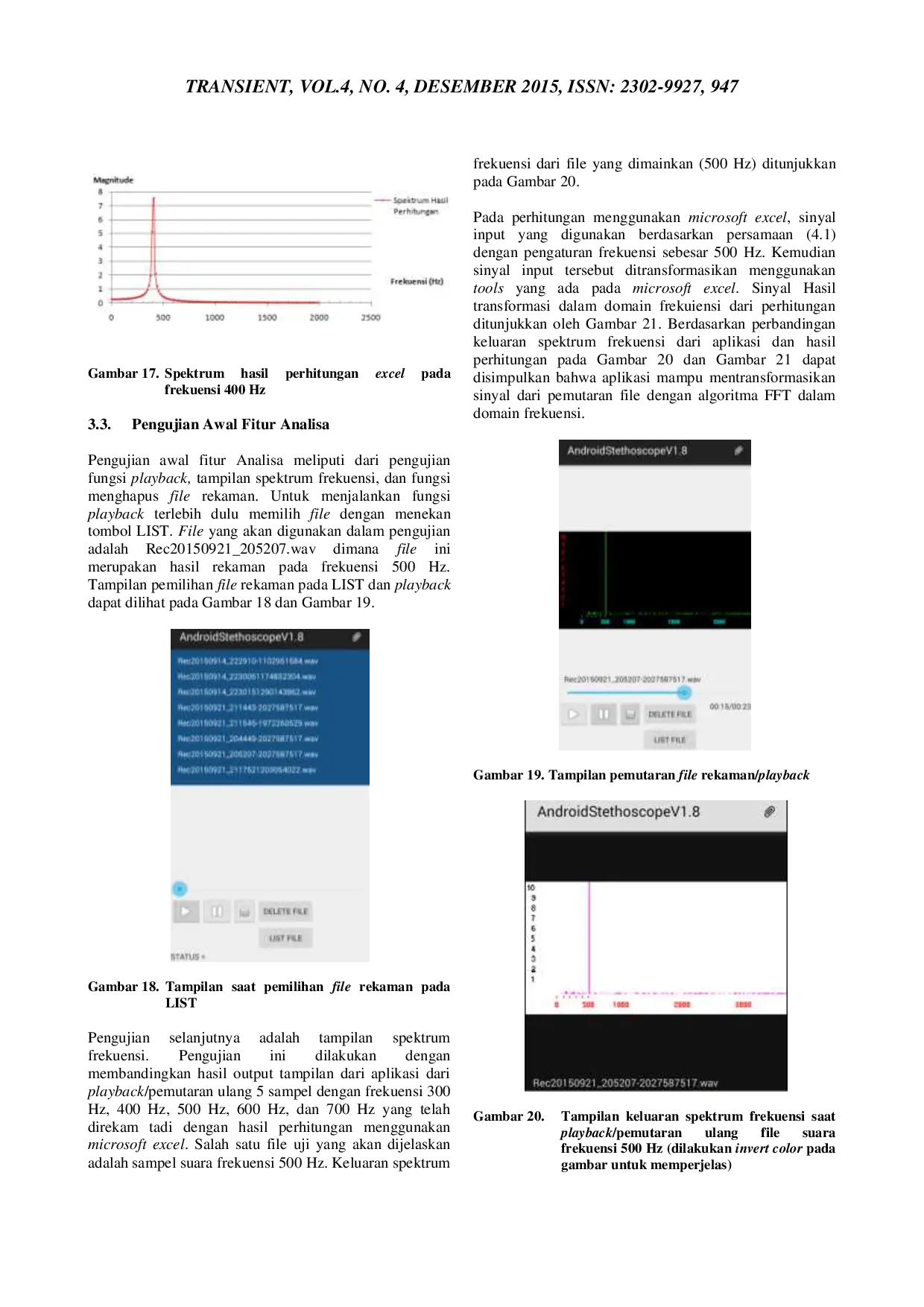

UNDIPUNDIP Suara jantung akan ditampilkan dalam bentuk spektrum frekuensi dengan metode Fast Fourier Transform menggunakan class RealDoubleFFT. java. Pada pengujianSuara jantung akan ditampilkan dalam bentuk spektrum frekuensi dengan metode Fast Fourier Transform menggunakan class RealDoubleFFT. java. Pada pengujian

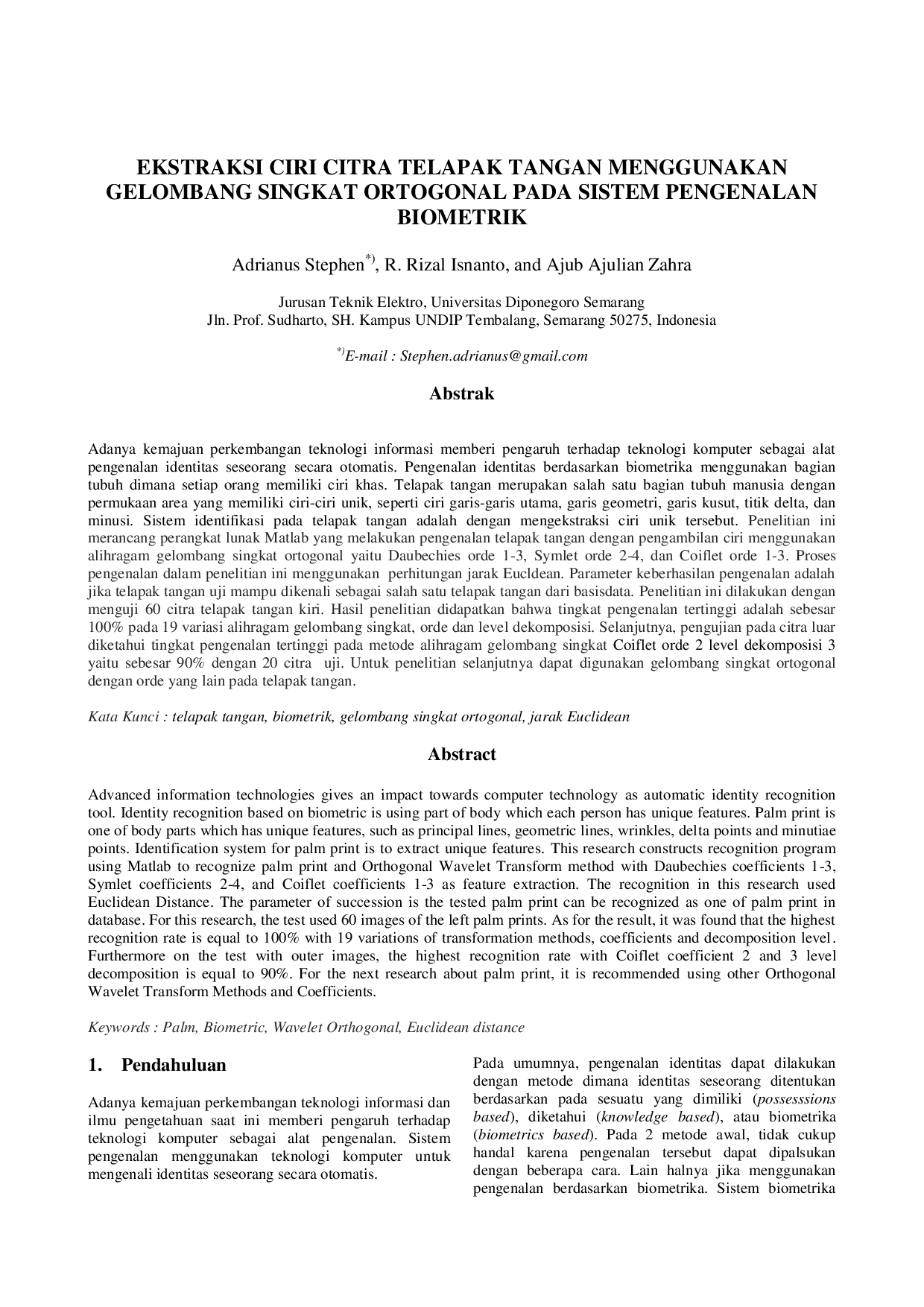

UNDIPUNDIP Sistem identifikasi pada telapak tangan adalah dengan mengekstraksi ciri unik tersebut. Penelitian ini merancang perangkat lunak Matlab yang melakukanSistem identifikasi pada telapak tangan adalah dengan mengekstraksi ciri unik tersebut. Penelitian ini merancang perangkat lunak Matlab yang melakukan

Useful /

UNKRISUNKRIS Selain itu juga belum optimalnya implementasi pemanfaatan ruang juga disebabkan kurangnya pengawasan dan pengendalian pemanfaatan ruang yang dilakukanSelain itu juga belum optimalnya implementasi pemanfaatan ruang juga disebabkan kurangnya pengawasan dan pengendalian pemanfaatan ruang yang dilakukan

STIKESSUAKAINSANSTIKESSUAKAINSAN 290/2008, namun masih ditemui hambatan berupa komunikasi yang tidak efektif, minimnya sosialisasi, keterbatasan SDM, serta kurangnya kesadaran pasien.290/2008, namun masih ditemui hambatan berupa komunikasi yang tidak efektif, minimnya sosialisasi, keterbatasan SDM, serta kurangnya kesadaran pasien.

UNDIPUNDIP Saat terjadi arching persentase penurunan kadar gas CO turun, arching terjadi pada tegangan 20kV yang hanya mampu mereduksi 2,7% berbeda jauh dengan kondisiSaat terjadi arching persentase penurunan kadar gas CO turun, arching terjadi pada tegangan 20kV yang hanya mampu mereduksi 2,7% berbeda jauh dengan kondisi

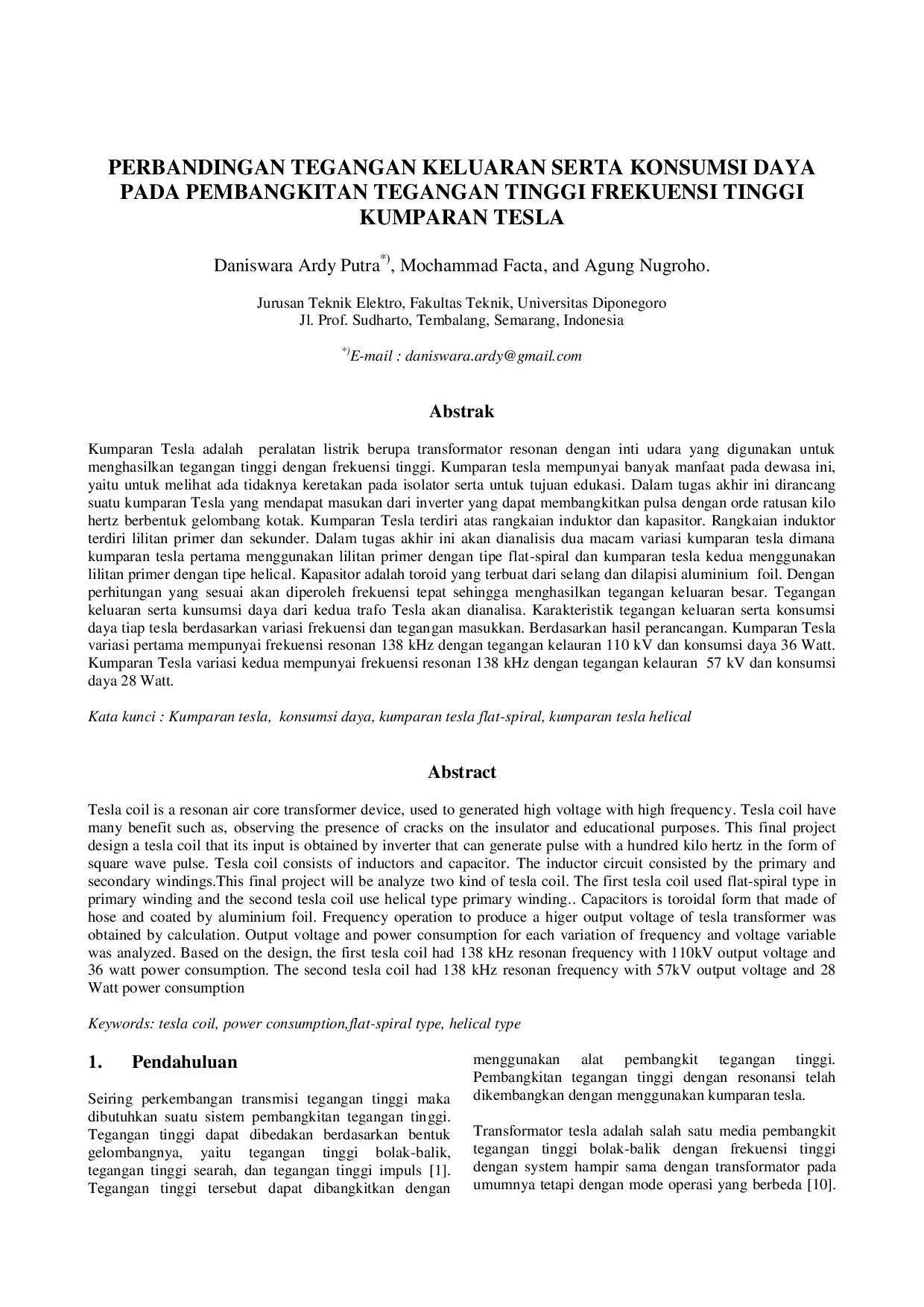

UNDIPUNDIP Dengan perhitungan yang sesuai akan diperoleh frekuensi tepat sehingga menghasilkan tegangan keluaran besar. Tegangan keluaran serta kunsumsi daya dariDengan perhitungan yang sesuai akan diperoleh frekuensi tepat sehingga menghasilkan tegangan keluaran besar. Tegangan keluaran serta kunsumsi daya dari