IAESCOREIAESCORE

International Journal of Electrical and Computer Engineering (IJECE)International Journal of Electrical and Computer Engineering (IJECE)Terdapat permintaan besar terhadap blok aritmatika berkecepatan tinggi, karena peningkatan kinerja unit pemrosesan. Untuk clock sistem dengan frekuensi tinggi, blok aritmatika harus mampu mengimbangi kebutuhan daya komputasi yang semakin besar. Area dan kecepatan umumnya merupakan kendala yang saling bertentangan, sehingga peningkatan kecepatan biasanya menghasilkan area yang lebih besar. Dalam penelitian ini, kami mencoba menentukan solusi terbaik untuk masalah ini dengan membandingkan hasil dari berbagai pengali. Berbagai ukuran dari dua algoritma untuk pengali perangkat keras berkecepatan tinggi dipelajari dan diimplementasikan, yaitu pengali paralel dan pengali bit serial. Kinerja kedua pengali ini dibandingkan dengan mengimplementasikan masing-masing secara terpisah dalam VHDL. Sejumlah desain pengali berkecepatan tinggi dikembangkan, dan algoritma serta desain pengali tersebut dibahas. Hasil penelitian ini akan membantu kita memilih opsi terbaik antara pengali serial dan paralel untuk pengali titik tetap dan titik mengambang yang akan difabrikasi dalam berbagai sistem. Karena pengali merupakan salah satu komponen paling penting dalam banyak sistem, menganalisis berbagai pengali akan membantu kita merancang sistem yang lebih baik dari segi area dan kecepatan.

Dua jenis pengali berbeda untuk perkalian titik tetap dan titik mengambang dirancang, diimplementasikan, dan dikaji.Analisis komparatif terhadap pengali tersebut menjadi kontribusi utama penelitian ini.Ditemukan bahwa seiring dengan peningkatan ukuran, delay dan area perangkat keras juga meningkat.Selain itu, pengali paralel memiliki area dan delay yang lebih besar dibandingkan pengali serial, sedangkan desain pengali paralel titik mengambang menempati area yang lebih kecil dibanding desain pengali bit serial titik tetap.

Pertama, perlu diteliti lebih lanjut bagaimana performa pengali bit serial dan paralel pada arsitektur 32-bit atau 64-bit untuk sistem dengan sumber daya terbatas, agar dapat diketahui efisiensi energi dan skalabilitasnya dalam aplikasi dunia nyata. Kedua, dapat dikembangkan studi komparatif yang memasukkan teknik optimasi seperti penggunaan carry-save adder atau Booth encoding pada kedua jenis pengali, untuk melihat pengaruhnya terhadap delay dan area tanpa mengubah pendekatan dasar dari masing-masing arsitektur. Ketiga, penting untuk mengevaluasi integrasi pengali titik mengambang 16-bit ke dalam sistem pemrosesan sinyal digital secara menyeluruh, termasuk dampaknya terhadap akurasi perhitungan dan throughput sistem secara keseluruhan dibandingkan dengan versi titik tetap, sehingga dapat memberikan panduan desain yang lebih komprehensif bagi rekayasa sistem digital di masa depan.

| File size | 118.02 KB |

| Pages | 9 |

| DMCA | Report |

Related /

UDBUDB Pengolahan data yaitu dengan cara pengumpulan data, koreksi data, klasifikasi, tabulasi, perhitungan dan penyajian data. Nilai BOR di RSUI Yakssi GemolongPengolahan data yaitu dengan cara pengumpulan data, koreksi data, klasifikasi, tabulasi, perhitungan dan penyajian data. Nilai BOR di RSUI Yakssi Gemolong

ALJAMIAHALJAMIAH Mereka mencoba untuk memahami bagian-bagian penting dari kisah-kisah tersebut dan menginterpretasikan nilai-nilai yang terkandung di dalam kisah tersebutMereka mencoba untuk memahami bagian-bagian penting dari kisah-kisah tersebut dan menginterpretasikan nilai-nilai yang terkandung di dalam kisah tersebut

HK PUBLISHINGHK PUBLISHING Narasi ini menimbulkan berbagai respons, termasuk kekhawatiran akan lunturnya semangat bela negara di kalangan mahasiswa. Penelitian ini bertujuan untukNarasi ini menimbulkan berbagai respons, termasuk kekhawatiran akan lunturnya semangat bela negara di kalangan mahasiswa. Penelitian ini bertujuan untuk

STIE AASSTIE AAS Secara keseluruhan, sistem pengendalian internal kas perusahaan tergolong baik dan mendukung integritas keuangan perusahaan. Prosedur penerimaan kas diSecara keseluruhan, sistem pengendalian internal kas perusahaan tergolong baik dan mendukung integritas keuangan perusahaan. Prosedur penerimaan kas di

JOIVJOIV Sejalan dengan perkembangan teknologi VR, YouTube menghadirkan fitur VR untuk mendukung penyebaran video realitas virtual di platformnya. Pada platformSejalan dengan perkembangan teknologi VR, YouTube menghadirkan fitur VR untuk mendukung penyebaran video realitas virtual di platformnya. Pada platform

KOMPETIFKOMPETIF Untuk memeriksa secara lebih detail kinerja pengusaha kuliner, peneliti melakukan survei terhadap manajer usaha dengan mengumpulkan data melalui kuesionerUntuk memeriksa secara lebih detail kinerja pengusaha kuliner, peneliti melakukan survei terhadap manajer usaha dengan mengumpulkan data melalui kuesioner

KOMPETIFKOMPETIF Variabel yang dianalisis meliputi kemandirian, modal, faktor emosional, dan pendidikan, dengan menggunakan teknik regresi linier berganda pada sampel sebanyakVariabel yang dianalisis meliputi kemandirian, modal, faktor emosional, dan pendidikan, dengan menggunakan teknik regresi linier berganda pada sampel sebanyak

IAESCOREIAESCORE Arsitektur berbasis multi-agen secara inheren memenuhi persyaratan tersebut melalui karakteristik seperti otonomi, desentralisasi, dan kemampuan pemantauan.Arsitektur berbasis multi-agen secara inheren memenuhi persyaratan tersebut melalui karakteristik seperti otonomi, desentralisasi, dan kemampuan pemantauan.

Useful /

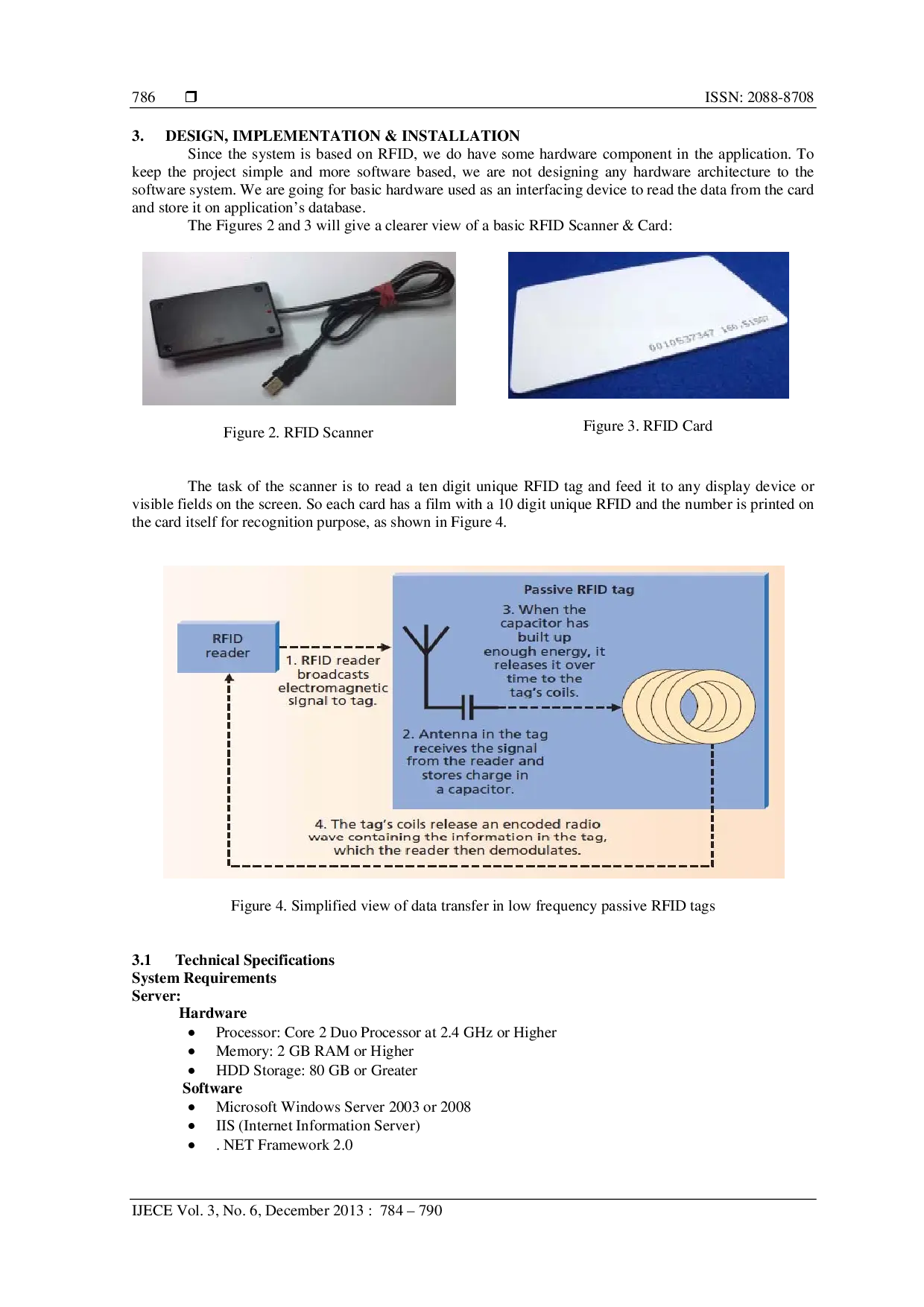

IAESCOREIAESCORE Untuk peningkatan keandalan, disarankan menambahkan indikator LCD atau kamera IP untuk mendeteksi kartu tidak terdaftar dan praktik buddy‑punching, sertaUntuk peningkatan keandalan, disarankan menambahkan indikator LCD atau kamera IP untuk mendeteksi kartu tidak terdaftar dan praktik buddy‑punching, serta

IAESCOREIAESCORE Sistem rekomendasi dirancang untuk memfasilitasi pencarian informasi pada situs web berskala besar secara otomatis, mengingat banyaknya faktor yang memengaruhiSistem rekomendasi dirancang untuk memfasilitasi pencarian informasi pada situs web berskala besar secara otomatis, mengingat banyaknya faktor yang memengaruhi

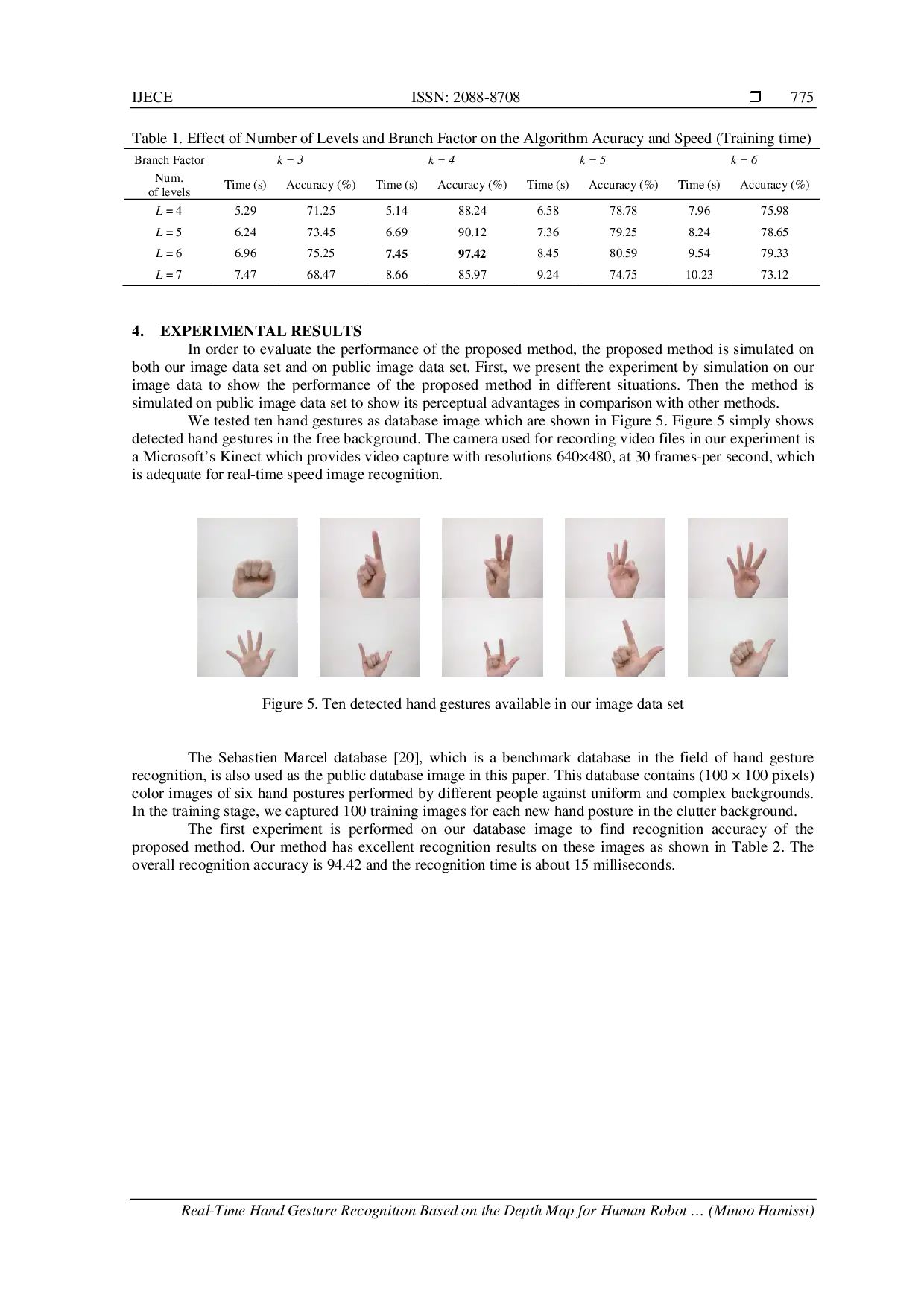

IAESCOREIAESCORE Metode pengenalan gerakan tangan berbasis sensor Kinect yang memanfaatkan citra kedalaman abu‑abu berhasil mendeteksi tangan secara independen dari latarMetode pengenalan gerakan tangan berbasis sensor Kinect yang memanfaatkan citra kedalaman abu‑abu berhasil mendeteksi tangan secara independen dari latar

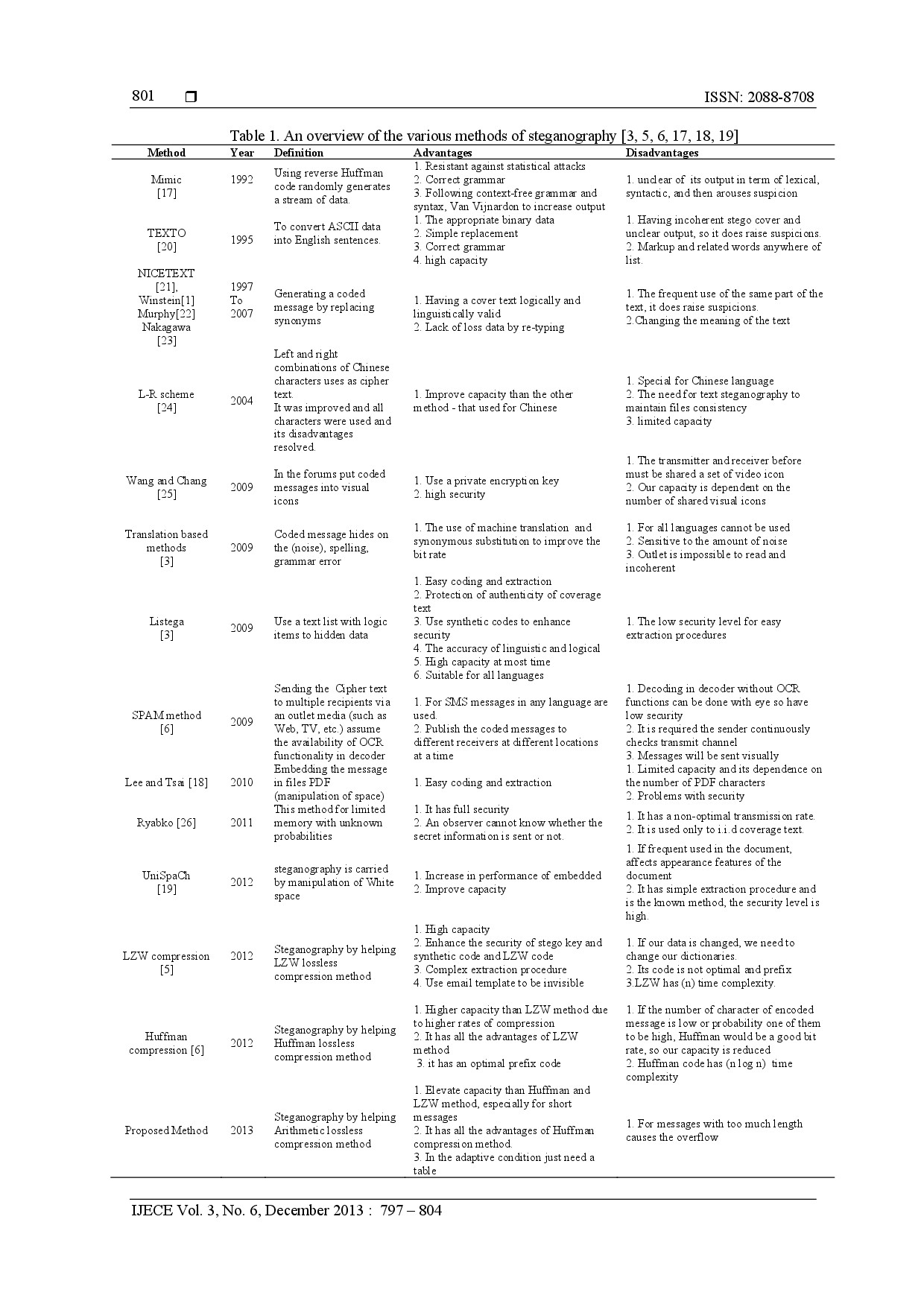

IAESCOREIAESCORE Hasil eksperimen menunjukkan peningkatan kapasitas sebesar 68,9 % dan keamanan terhadap serangan pasif sebesar 82,88 % dibandingkan pendekatan sebelumnya,Hasil eksperimen menunjukkan peningkatan kapasitas sebesar 68,9 % dan keamanan terhadap serangan pasif sebesar 82,88 % dibandingkan pendekatan sebelumnya,