LAPANLAPAN

Jurnal Teknologi DirgantaraJurnal Teknologi DirgantaraSalah satu fungsi sistem Payload Data Handling (PDH) pada sebuah satelit adalah melakukan channel coding untuk data citra satelit. Consultative Committee for Space Data Systems (CCSDS) telah merekomendasikan penggunaan encoder Reed-Solomon (RS) untuk keperluan channel coding tersebut. Untuk dapat merealisasikan transmisi dengan laju data yang tinggi, maka implementasi algoritma encoder RS pada sitem PDH satelit membutuhkan Field Programmable Gate Array (FPGA). Penelitian ini bertujuan untuk merancang modul encoder RS(255,223) berbasis CCSDS dan mengimplementasikan encoder tersebut pada FPGA dengan desain rangkaian yang lebih optimal dibandingkan dengan encoder RS komersial (IP-core). Berdasarkan hasil pengujian yang telah dilakukan, encoder yang dirancang memiliki beberapa kelebihan dalam hal efisiensi gerbang logika yang digunakan dan tingkat kinerja data keluaran yang dihasilkan. Selain itu, pada penelitian ini juga dikembangkan metode encoding paralel yang akan diterapkan pada sistem PDH satelit. Hasil pengujian menunjukkan bahwa dengan menggunakan metode tersebut, data keluaran yang dihasilkan encoder memiliki laju data yang lebih tinggi dan tidak membutuhkan data dummy untuk melengkapi data keluaran. Kedua hasil tersebut diharapkan dapat mendukung pengembangan sistem PDH satelit yang dilakukan di Pusat Teknologi Satelit saat ini.

Penelitian ini berhasil merancang modul encoder RS(255,223) berbasis CCSDS yang memiliki kinerja lebih baik dan efisiensi gerbang logika lebih tinggi dibandingkan encoder komersial.Encoder dengan metode encoding paralel mampu meningkatkan laju data keluaran dan menghilangkan kebutuhan data dummy.Namun, sistem ini membutuhkan lebih banyak gerbang logika karena menggunakan lima encoder secara paralel, sehingga perlu dilakukan optimasi lebih lanjut untuk meminimalkan penggunaan gerbang logika tanpa mengorbankan kinerja.

Pertama, perlu dikembangkan penelitian untuk merancang arsitektur encoder RS(255,223) yang lebih ringkas dengan mengoptimalkan struktur gerbang logika perkalian di Galois Field, sehingga jumlah gerbang logika kombinasional dapat ditekan tanpa mengurangi kecepatan pemrosesan. Kedua, perlu dilakukan studi tentang penggunaan teknik time-multiplexing pada sistem encoding paralel agar lima proses encoding dapat berbagi satu atau beberapa modul encoder secara efisien, sehingga mengurangi kebutuhan gerbang logika namun tetap mempertahankan kecepatan tinggi tanpa data dummy. Ketiga, perlu diuji penerapan metode encoding paralel ini pada format interleave lain selain interleave-5, seperti interleave-3 atau interleave-7, untuk mengetahui apakah skema paralelisasi yang dirancang dapat diterapkan secara fleksibel pada berbagai tingkat interleaving, yang mendukung kompatibilitas dengan berbagai standar transmisi satelit.

| File size | 1.13 MB |

| Pages | 12 |

| DMCA | ReportReport |

Related /

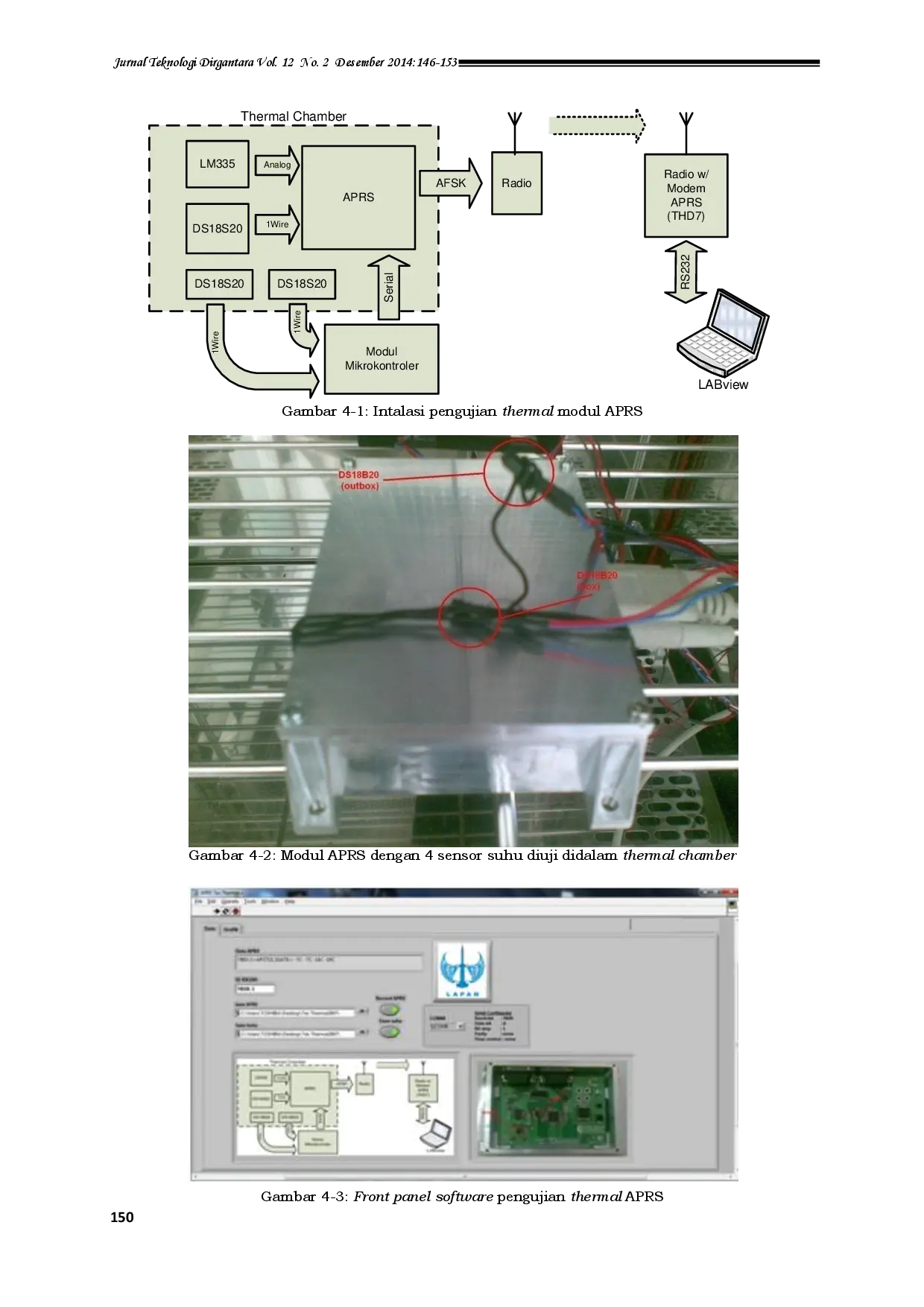

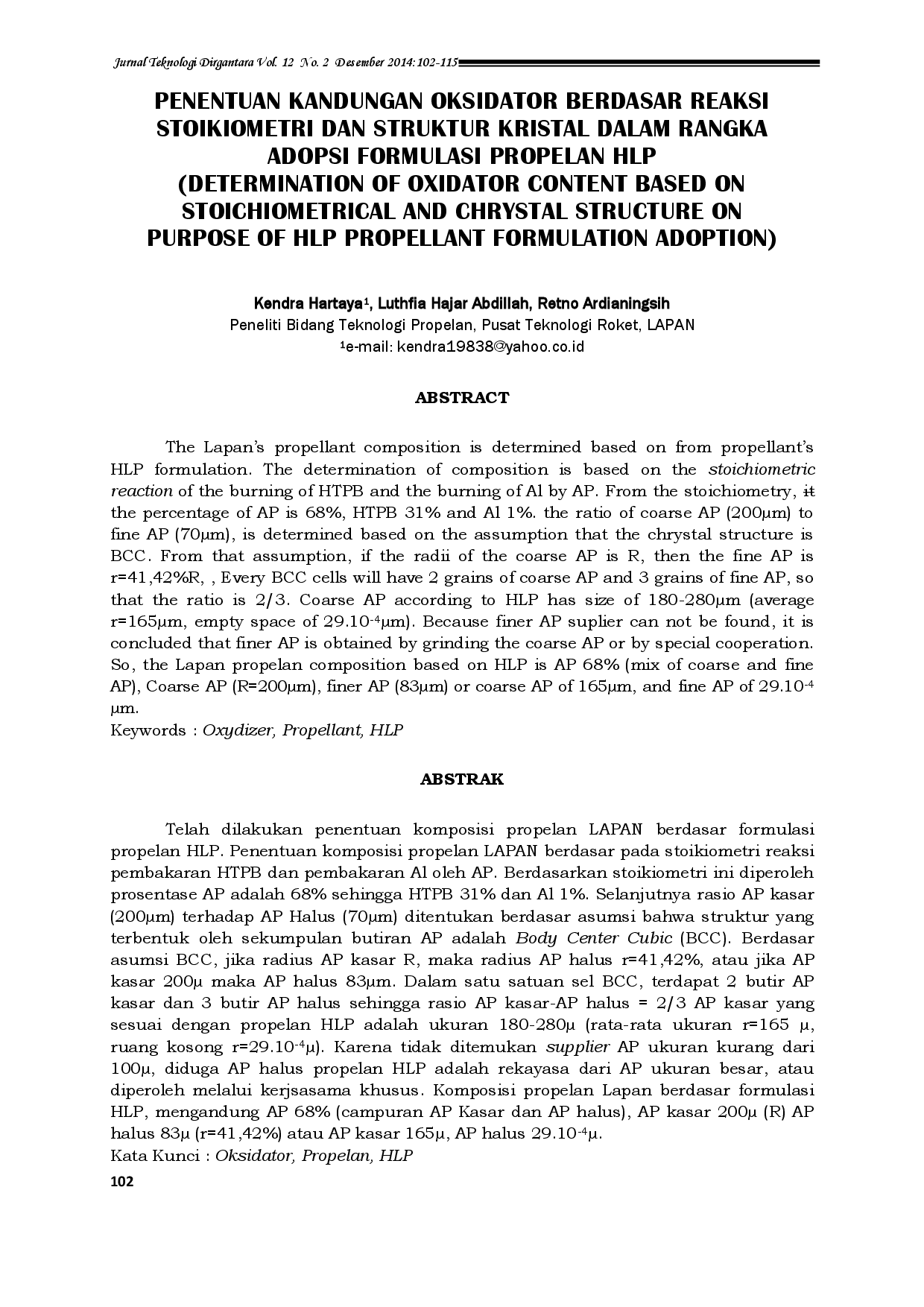

LAPANLAPAN Hasil akhir yang berupa grafik temperatur terhadap waktu menunjukkan bahwa dengan menggunakan rentang kesalahan ±1°C, sensor analog dari modul APRS kurangHasil akhir yang berupa grafik temperatur terhadap waktu menunjukkan bahwa dengan menggunakan rentang kesalahan ±1°C, sensor analog dari modul APRS kurang

LAPANLAPAN Komposisi propelan Lapan berdasarkan formulasi HLP, mengandung AP 68% (campuran AP Kasar dan AP halus), AP kasar 200µ (R) AP halus 83µ (r=41,42%) atauKomposisi propelan Lapan berdasarkan formulasi HLP, mengandung AP 68% (campuran AP Kasar dan AP halus), AP kasar 200µ (R) AP halus 83µ (r=41,42%) atau

STIE AASSTIE AAS Oleh karena itu, disarankan kepada semua karyawan untuk terus memperkuat etos kerja, menciptakan lingkungan kerja yang kondusif, dan menginternalisasiOleh karena itu, disarankan kepada semua karyawan untuk terus memperkuat etos kerja, menciptakan lingkungan kerja yang kondusif, dan menginternalisasi

STIE AASSTIE AAS Hasil penelitian menunjukkan bahwa prosedur penerimaan kas telah diterapkan sesuai teori dan standar pengendalian internal, mencakup pembayaran, rekonsiliasiHasil penelitian menunjukkan bahwa prosedur penerimaan kas telah diterapkan sesuai teori dan standar pengendalian internal, mencakup pembayaran, rekonsiliasi

Useful /

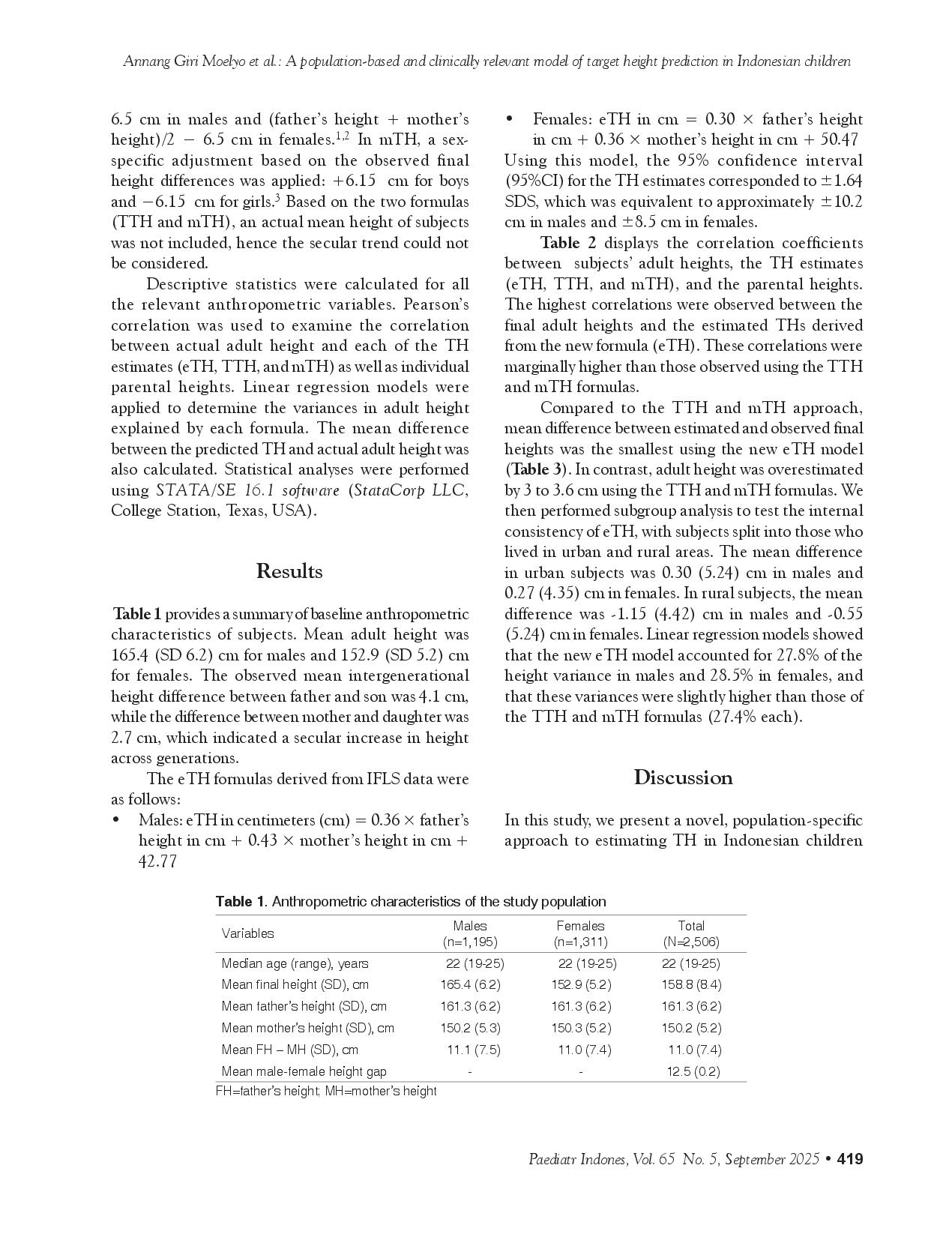

PAEDIATRICAINDONESIANAPAEDIATRICAINDONESIANA Hasil studi menunjukkan bahwa model eTH memiliki kinerja yang lebih baik dibandingkan dengan rumus tradisional, dengan koefisien korelasi yang lebih tinggiHasil studi menunjukkan bahwa model eTH memiliki kinerja yang lebih baik dibandingkan dengan rumus tradisional, dengan koefisien korelasi yang lebih tinggi

STIE AASSTIE AAS Kemampuan jaringan (NSNC) memiliki pengaruh terbesar terhadap kinerja pasar internasional (IMP), diikuti oleh pengetahuan pasar internasional (FMK) danKemampuan jaringan (NSNC) memiliki pengaruh terbesar terhadap kinerja pasar internasional (IMP), diikuti oleh pengetahuan pasar internasional (FMK) dan

STIE AASSTIE AAS Karyawan memiliki persepsi positif terhadap kesejahteraan kerja secara keseluruhan, terutama terkait pemenuhan kebutuhan dasar seperti makanan, tempatKaryawan memiliki persepsi positif terhadap kesejahteraan kerja secara keseluruhan, terutama terkait pemenuhan kebutuhan dasar seperti makanan, tempat

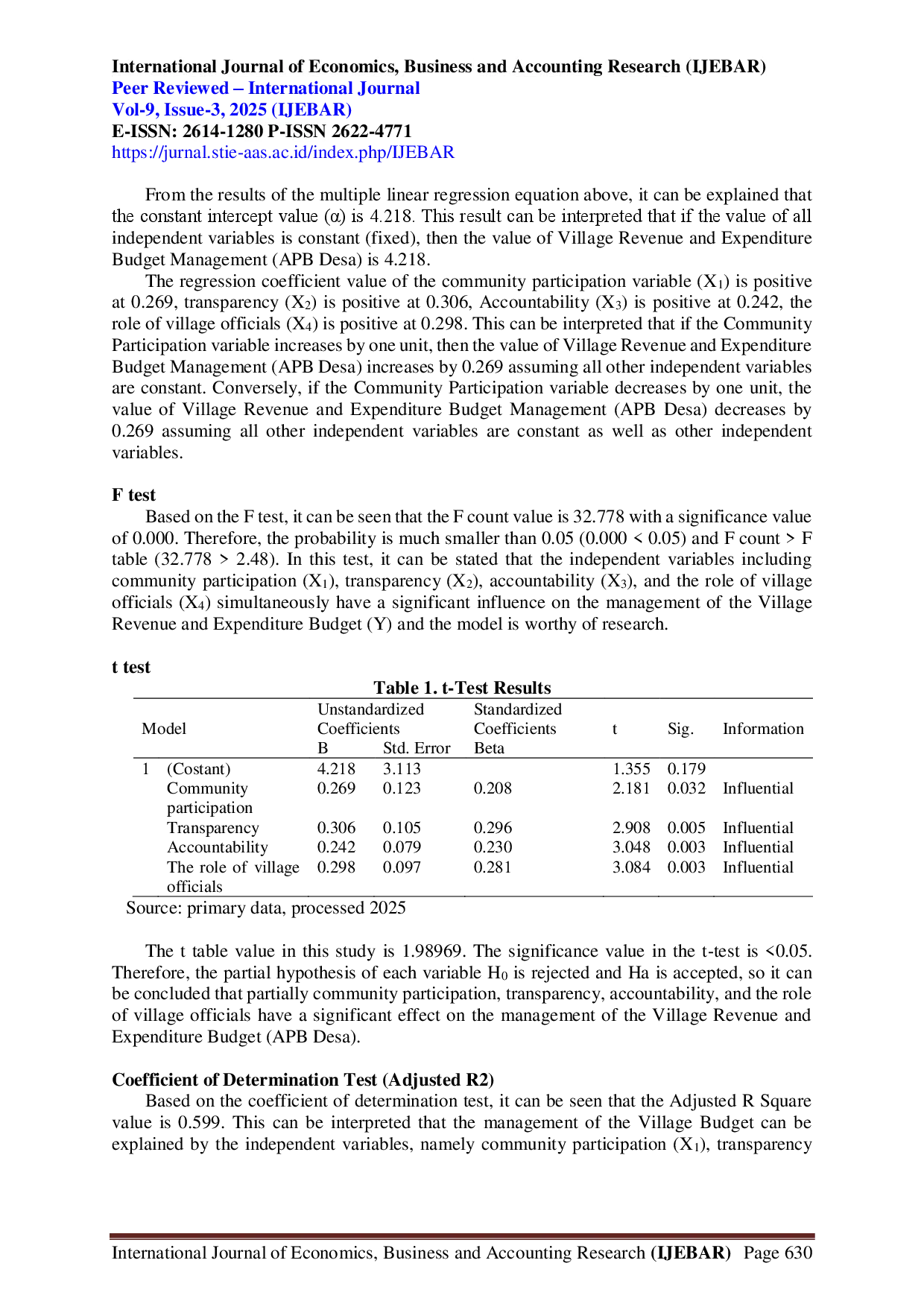

STIE AASSTIE AAS Populasi dalam penelitian ini meliputi Kepala Desa, Aparat Desa, dan Badan Permusyawaratan Desa (sebagai perwakilan masyarakat) di desa‑desa KecamatanPopulasi dalam penelitian ini meliputi Kepala Desa, Aparat Desa, dan Badan Permusyawaratan Desa (sebagai perwakilan masyarakat) di desa‑desa Kecamatan