IAESCOREIAESCORE

International Journal of Electrical and Computer Engineering (IJECE)International Journal of Electrical and Computer Engineering (IJECE)Makalah ini menyajikan rancangan dan implementasi demodulator BPSK dan sinkronisasi bit yang dapat diprogram. Demodulator didasarkan pada desain loop Costas, sedangkan sinkronisasi bit didasarkan pada detektor kesalahan waktu Gardner. Kelebihan dari desain ini adalah bahwa itu menawarkan kemampuan penggunaan multirate dan tidak bergantung pada perhitungan koefisien filter, sudut input NCO untuk setiap tingkat data tertentu, sehingga menghindari kompleksitas komputasi.

Sebuah rancangan dan pengembangan demodulator BPSK-bit sinkronizer yang dapat diprogram menggunakan pengolahan multirate telah ditunjukkan.Dalam penelitian ini, telah dibuktikan bahwa demodulator dan sinkronisasi bit dapat diprogram untuk berbagai tingkat data dari 1 kbps hingga 8 kbps.Penelitian ini juga menunjukkan bahwa kebutuhan clock yang lebih tinggi dapat dioptimalkan lebih lanjut dengan mengimplementasikan filter FIR dengan paralelisme yang lebih tinggi dan membuat sinkronisasi bit bekerja dengan dua sampel per bit.

Penelitian ini dapat diteruskan dengan mengembangkan demodulator BPSK-bit sinkronizer yang dapat diprogram untuk frekuensi pembawa yang berbeda dan tingkat data yang lebih tinggi. Selain itu, penelitian juga dapat dilakukan untuk mengoptimalkan kebutuhan clock dan mengembangkan FILTER yang lebih efisien. Dengan demikian, penelitian ini dapat memberikan kontribusi pada pengembangan sistem komunikasi yang lebih effisien dan efektif.

| File size | 242.07 KB |

| Pages | 8 |

| DMCA | ReportReport |

Related /

IAESCOREIAESCORE Tujuan paper ini adalah mengusulkan pendekatan analisis sistem berbasis metode OOPP (Objective Oriented Project Planning) untuk sistem energi terbarukanTujuan paper ini adalah mengusulkan pendekatan analisis sistem berbasis metode OOPP (Objective Oriented Project Planning) untuk sistem energi terbarukan

IAESCOREIAESCORE Perangkat lunak ini menyediakan antarmuka yang ramah pengguna untuk membantu mahasiswa menganalisis mesin listrik, di mana pengguna dapat memilih pengujianPerangkat lunak ini menyediakan antarmuka yang ramah pengguna untuk membantu mahasiswa menganalisis mesin listrik, di mana pengguna dapat memilih pengujian

IAESCOREIAESCORE Hasil eksperimen menunjukkan bahwa teknik enkripsi yang diusulkan efektif dan memiliki fitur keamanan yang tinggi. Teori chaos terbukti merupakan kandidatHasil eksperimen menunjukkan bahwa teknik enkripsi yang diusulkan efektif dan memiliki fitur keamanan yang tinggi. Teori chaos terbukti merupakan kandidat

IAESCOREIAESCORE The significant load required in formation of a workpiece is one of the existing constraints for the reverse extrusion process. This issue becomes ratherThe significant load required in formation of a workpiece is one of the existing constraints for the reverse extrusion process. This issue becomes rather

Useful /

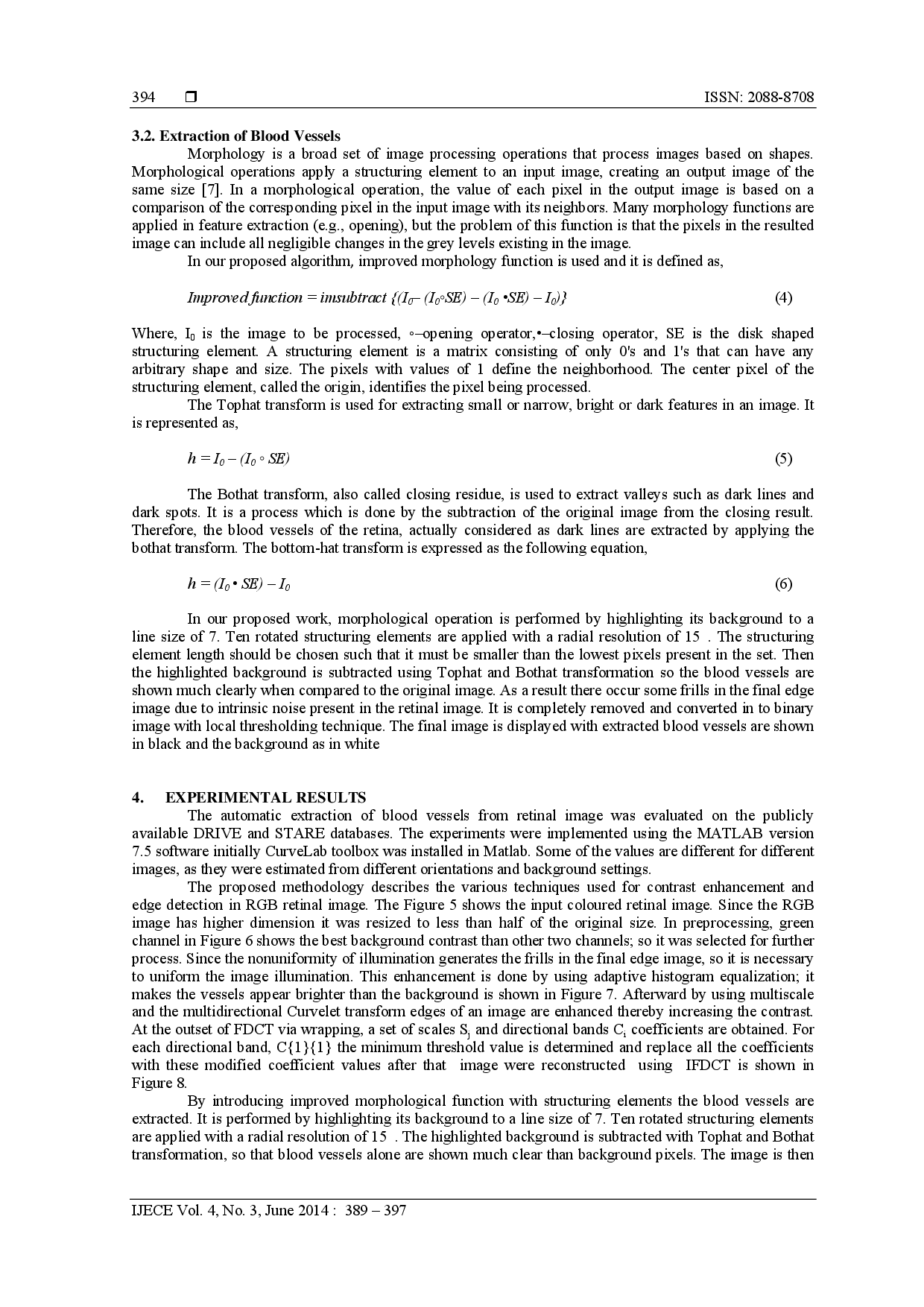

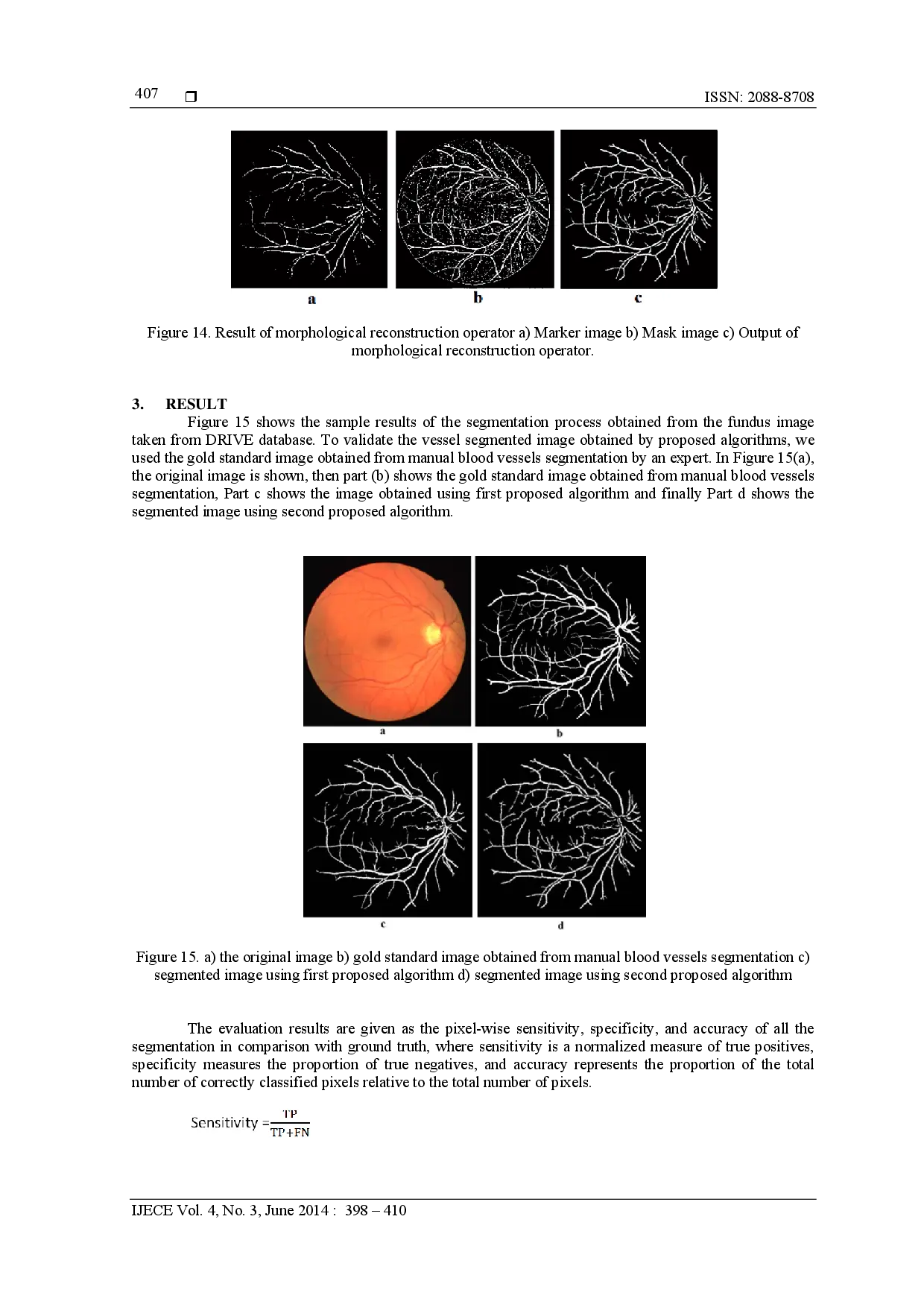

IAESCOREIAESCORE Selanjutnya, transformasi Curvelet dimanfaatkan untuk meningkatkan kontras dengan menonjolkan tepi citra pada berbagai skala dan arah. Terakhir, fungsiSelanjutnya, transformasi Curvelet dimanfaatkan untuk meningkatkan kontras dengan menonjolkan tepi citra pada berbagai skala dan arah. Terakhir, fungsi

IAESCOREIAESCORE Hasil menunjukkan bahwa algoritma kami sangat efektif dalam mendeteksi pembuluh darah retina. Kami mengusulkan dua metode segmentasi pembuluh darah retina.Hasil menunjukkan bahwa algoritma kami sangat efektif dalam mendeteksi pembuluh darah retina. Kami mengusulkan dua metode segmentasi pembuluh darah retina.

IAESCOREIAESCORE Berbagai jenis rasio silang terjadi pada jaringan listrik. Perubahan rezim operasi pada jaringan tertentu atau perubahan parameter jaringan menghasilkanBerbagai jenis rasio silang terjadi pada jaringan listrik. Perubahan rezim operasi pada jaringan tertentu atau perubahan parameter jaringan menghasilkan

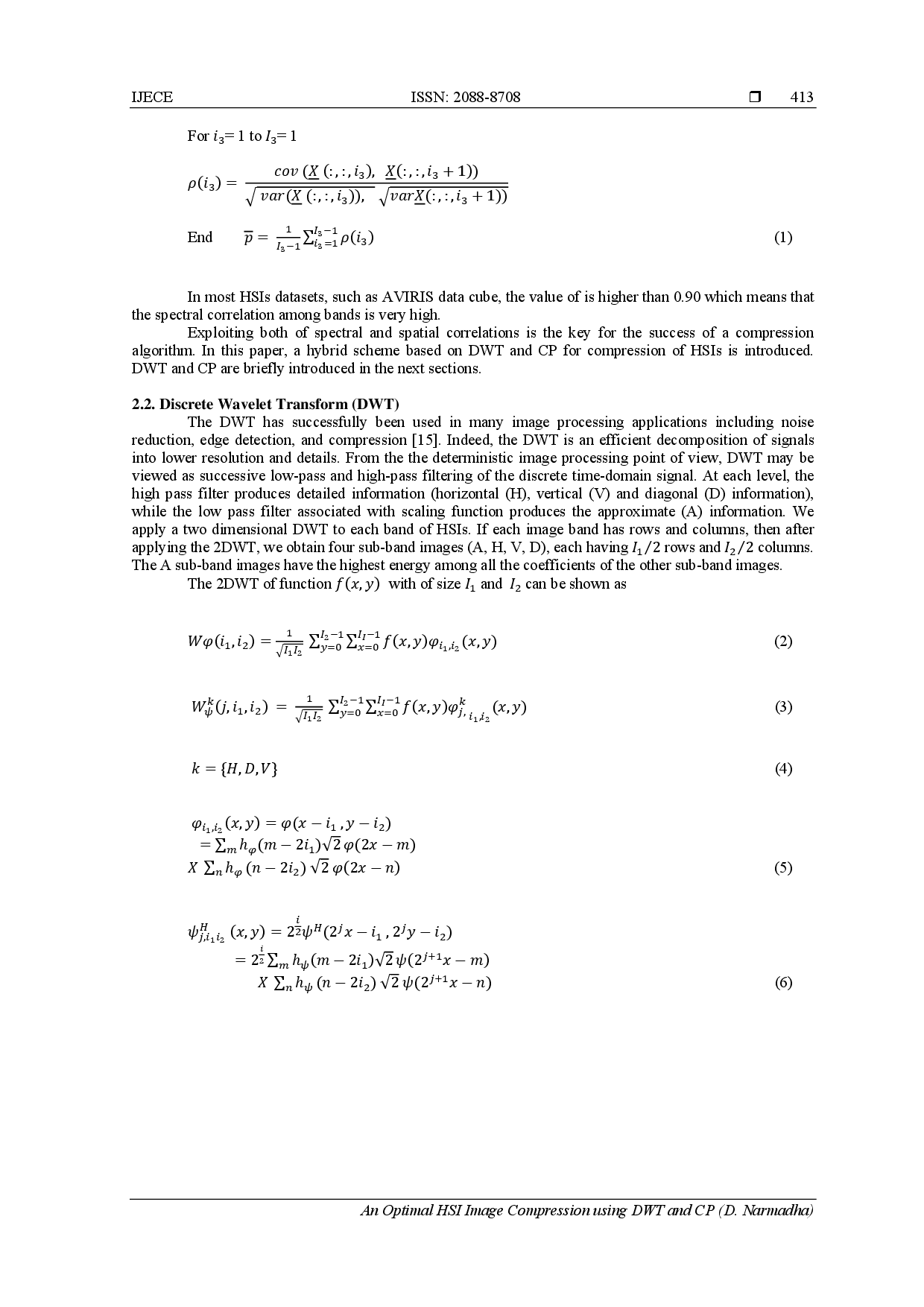

IAESCOREIAESCORE Metode efisien untuk kompresi citra hiperspektral disajikan. Algoritma yang diusulkan, berdasarkan Discrete Wavelet Transform dan CANDECOM/PARAFAC (DWT-CP),Metode efisien untuk kompresi citra hiperspektral disajikan. Algoritma yang diusulkan, berdasarkan Discrete Wavelet Transform dan CANDECOM/PARAFAC (DWT-CP),